Electronic components and materials

## PHILIPS

## Buyers & engineers guide

# MEMORIES AND MICROPROCESSORS bipolar and MOS

## CONTENTS

JFP PHILIPSE 7-11-1978

|                 | 25                             |                |                                    |

|-----------------|--------------------------------|----------------|------------------------------------|

| MEMORIES        | type index                     | bipolar<br>MOS | page<br>2 — 3<br>4 — 5             |

|                 | cross reference                | bipolar<br>MOS | 6 — 7<br>8 — 9                     |

|                 | technical data                 | bipolar<br>MOS | 10 — 15<br>16 — 18                 |

|                 | pin diagrams<br>second sources | bipolar<br>MOS | 19 — 29<br>30 — 43                 |

| MICROPROCESSORS | type index                     |                | 44                                 |

|                 | cross reference                |                | 44                                 |

|                 | technical data                 | bipolar<br>MOS | <b>45 - 57</b><br><b>58 - 1</b> 08 |

|                 | documentation; courses         |                | 109 - 111                          |

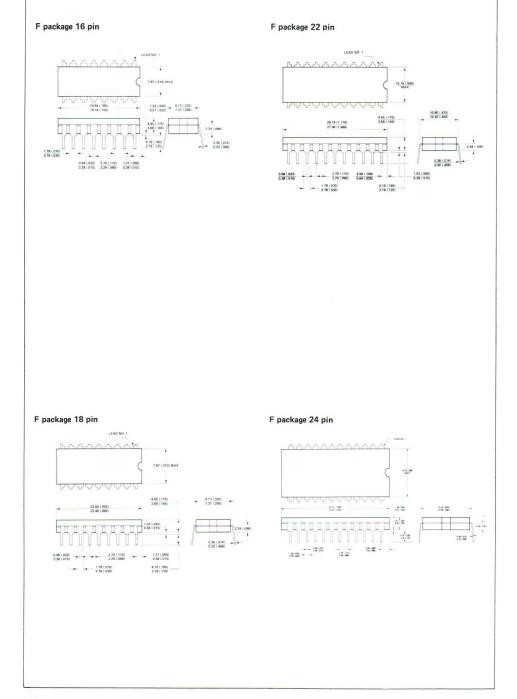

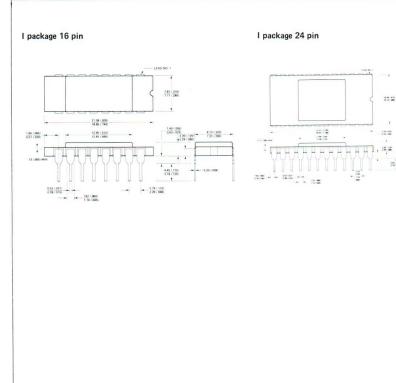

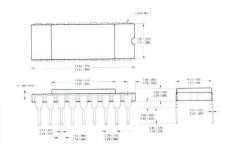

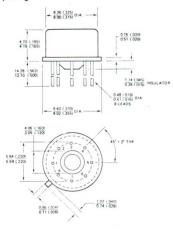

| PACKAGES        |                                |                | 113 – 116                          |

| WHEN ORDERING | please quote the ordering code to specify device, temperature range<br>if applicable (prefix N or S), and package (suffix D, E, F, I, K, N, P, T<br>or TA).                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | examples:                                                                                                                                                                                                                                  |

|               | N82S25N commercial temperature range, plastic DLL package<br>S82S16F military temperature range, cerdip DLL package<br>N74S89N commercial temperature range, plastic DLL package<br>S54S89F military temperature range, cerdip DLL package |

|               | 26501 commercial temperature range metal ceramic DLL package                                                                                                                                                                               |

## type index

#### Bipolar

|            | RAM      |          |         | PROM     |               |      |

|------------|----------|----------|---------|----------|---------------|------|

| technology | capacity | type     | page    | capacity | type p        | bage |

| TTL        | 16 × 4   | N3101A   | 10 - 11 | 32 x 8   | N82S23 12 -   | - 13 |

|            | 16 x 4   | N74S89   |         | 32 x 8   | N82S123       |      |

|            | 16 × 4   | N74S189  |         | 256 × 4  | N82S27        |      |

|            | 16 x 4   | N82S25   |         | 256 x 4  | N82S126       |      |

|            | 256 × 1  | N74S200  |         | 256 x 4  | N82S129       |      |

|            | 256 x 1  | N74S201  |         | 256 x 8  | N82S114       |      |

|            | 256 x 1  | N74S301  |         | 512 x 4  | N82S130       |      |

|            | 256 x 1  | N82S16   |         | 512 x 4  | N82S131       |      |

|            | 256 x 1  | N82S116  |         | 512 x 8  | N82S115       |      |

|            | 256 x 1  | N82S17   |         | 512 x 8  | N82S140       |      |

|            | 256 x 1  | N82S117  |         | 512 x 8  | N82S141       |      |

|            | 64 x 9   | N82S09   |         | 512 x 8  | N82S146       |      |

|            | 1k x 1   | N82S10   |         | 512 x 8  | N82S147       |      |

|            | 1k x 1   | N93415A  |         | 1k x 4   | N82S136       |      |

|            | 1k x 1   | N82S110  |         | 1k x 4   | N82S137       |      |

|            | 1k x 1   | N82LS10  |         | 1k x 8   | N82S180       |      |

|            | 1k x 1   | N82S11   |         | 1k x 8   | N82S181       |      |

|            | 1k x 1   | N93425A  |         | 1k x 8   | N82S2708      |      |

|            | 1k x 1   | N82S111  |         | 2k x 4   | N82S184       |      |

|            | 1k x 1   | N82LS11  |         | 2k x 4   | N82S185       |      |

|            | 256 x 8  | N82S208  |         | 2k x 8   | N82S190       |      |

|            | 256 x 9  | N82S210  |         | 2k x 8   | N82S191       |      |

|            | 4k x 1   | N82S400  |         |          |               |      |

|            | 4k x 1   | N82S401  |         |          |               |      |

|            |          |          |         |          |               |      |

| ECL        | 16 × 4   | GXB10145 | 14 - 15 | 32 × 8   | GXB10139 14 - | - 15 |

|            | 64 × 1   | GXB10140 |         | 256 x 4  | GXB10149      |      |

|            | 64 × 1   | GXB10142 |         |          |               |      |

|            | 64 × 1   | GXB10148 |         |          |               |      |

|            | 128 x 1  | GXB10405 |         |          |               |      |

|            | 256 x 1  | GXB10144 |         |          |               |      |

|            | 256 x 1  | GXB10410 |         |          |               |      |

|            | 1k x 1   | GXB10415 |         |          |               |      |

|            | ROM      |         |         | specials    |      |         |         |

|------------|----------|---------|---------|-------------|------|---------|---------|

| technology | capacity | type    | page    | capacity    |      | type    | page    |

| TTL        | 256 × 4  | N82S226 | 14 - 15 | 8 x 4       | SAM  | N82S12  | 14 - 15 |

|            | 256 x 4  | N82S229 |         | 8 x 4       | SAM  | N82S112 |         |

|            | 256 × 8  | N82S214 |         | 32 x 2      | WWRM | N82S21  |         |

|            | 512 × 4  | N82S230 |         | 16 x 48 x 8 | FPLA | N82S100 |         |

|            | 512 × 4  | N82S231 |         | 16 x 48 x 8 | FPLA | N82S101 |         |

|            | 512 × 8  | N82S215 |         | 16 x 9      | FPGA | N82S102 |         |

|            | 512 x 8  | N82S240 |         | 16 x 9      | FPGA | N82S103 |         |

|            | 512 x 8  | N82S241 |         | 16 x 48 x 8 | FPLA | N82S106 |         |

|            | 1k x 4   | N8228   |         | 16 x 48 x 8 | FPLA | N82S107 |         |

|            | 1k x 8   | N82S280 |         | 16 x 48 x 8 | PLA  | N82S200 |         |

|            | 1k x 8   | N82S281 |         | 16 x 48 x 8 | PLA  | N82S201 |         |

|            | 2k x 8   | N82S290 |         |             |      |         |         |

|            | 2k × 8   | N82S291 |         |             |      |         |         |

|            |          |         |         |             |      |         |         |

ECL

8 x 2 CAM GXB10155 14 - 15

type index

MOS

|            | RAM      |            |         | EPROM    |      |        |

|------------|----------|------------|---------|----------|------|--------|

| technology | capacity | type       | page    | capacity | type | pag    |

| MOS        | static   |            |         |          |      |        |

|            | 256 x 1  | 2501       | 16 - 17 | 4k       | 2704 | 16 - 1 |

|            | 256 x 1  | 25L01      |         | 8k       | 2708 |        |

|            | 256 x 1  | HEF4720B(V | /)      |          |      |        |

|            | 256 x 4  | 2101       |         |          |      |        |

|            | 256 x 4  | 2111       |         |          |      |        |

|            | 256 x 4  | 2112       |         |          |      |        |

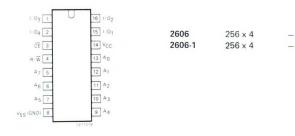

|            | 256 x 4  | 2606       |         |          |      |        |

|            | 256 x 4  | 2606-1     |         |          |      |        |

|            | 1k x 1   | 2102       |         |          |      |        |

|            | 1k x 1   | 21F02      |         |          |      |        |

|            | 1k x 1   | 21L02      |         |          |      |        |

|            | 1k x 1   | 2102A/AL   |         |          |      |        |

|            | 1k x 1   | 2115       |         |          |      |        |

|            | 1k x 1   | 2125       |         |          |      |        |

|            | 1k x 4   | 2614       |         |          |      |        |

|            | 1k x 4   | 2624       |         |          |      |        |

|            | 4k x 1   | 2613       |         |          |      |        |

|            | 4k x 1   | 2623       |         |          |      |        |

|            | dynamic  |            |         |          |      |        |

|            | 4k x 1   | 2627       | 16 - 17 |          |      |        |

|            | 4k x 1   | 2660       |         |          |      |        |

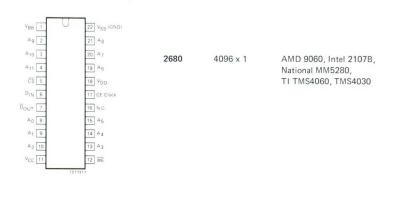

|            | 4k x 1   | 2680       |         |          |      |        |

|            | 16k x 1  | 2690       |         |          |      |        |

|      |      | shift registers |         |       |                      |            |

|------|------|-----------------|---------|-------|----------------------|------------|

| page | type | capacity        | page    | type  | capacity             | technology |

|      |      | static          |         |       | ROM                  | MOS        |

| 18   | 2509 | 2 x 50          | 16 - 17 | 2530  | 512 x 8              |            |

|      | 2518 | 6 x 32          |         | 2607  | 1k x 8               |            |

|      | 2510 | 2 × 100         |         | 2608  | 1k x 8               |            |

|      | 2519 | 6 × 40          |         | 2580  | 2k x 4               |            |

|      | 2521 | 2 x 128         |         | 2600  | 2k x 8               |            |

|      | 2522 | 2 x 132         |         | 2616  | 2k x 8               |            |

|      | 2532 | 4 × 80          |         | 2617  | 2k x 8               |            |

|      | 2511 | 2 × 200         |         |       |                      |            |

|      | 2529 | 2 x 240         |         |       |                      |            |

|      | 2528 | 2 x 250         |         |       |                      |            |

|      | 2527 | 2 x 256         |         |       |                      |            |

|      | 2533 | 1 x 1k          |         |       |                      |            |

|      |      | dynamic         |         | ators | character generation |            |

| 18   | 2506 | 2 x 100         | 16 - 17 | 2513  | 64 x 8 x 5           |            |

|      | 2507 | 2 x 100         |         | 2516  | 64 x 6 x 8           |            |

|      | 2517 | 2 × 100         |         | 2526  | 64 x 9 x 9           |            |

|      | 2505 | 1 x 512         |         | 2609  | 128 x 7 x 9          |            |

|      | 2524 | 1 x 512         |         |       |                      |            |

|      | 2502 | 4 x 256         |         |       |                      |            |

|      | 2503 | 2 x 512         |         |       |                      |            |

|      | 2504 | 1 x 1k          |         |       |                      |            |

|      | 2512 | 1 x 1k          |         |       |                      |            |

|      | 2525 | 1 x 1k          |         |       |                      |            |

### cross reference

#### Bipolar

| Liser Plant R.                                                      |                                                            |                                                        |                                                                |                                                      |                                                             |

|---------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|

| AMD                                                                 | Signetics                                                  | Fairchild                                              | Signetics                                                      | Harris                                               | Signetics                                                   |

| 2700/27LS00<br>2701/27LS01<br>27S08/27LS08<br>27S09/27LS09<br>27S10 | 82S16<br>82S17<br>82S23<br>82S123<br>82S126                | 10405<br>10410<br>10415<br>10145A<br>10149             | GXB10405<br>GXB10410/10144<br>GXB10415<br>GXB10145<br>GXB10149 | 0064<br>1024/HM7610<br>1024A/HM7611<br>2048<br>2048A | 82S25<br>82S129<br>82S126<br>82S131<br>82S130               |

| 27S11<br>2952<br>2953<br>2980<br>2981                               | 825129<br>82510/93415A<br>82511/93425A<br>825101<br>825100 | 93403<br>93406<br>93410<br>93411<br>93411A             | 82S25<br>82S226<br>74S301<br>82S17<br>82S117                   | HM7602/8256<br>HM7603<br>HM7615<br>HM7620<br>HM7621  | 82S23<br>82S123<br>GXB10149<br>82S130<br>82S131             |

| 3101<br>3101A/27S02                                                 | 82S25<br>3101A                                             | 93415<br>93415A<br>93415B<br>93L415<br>93417           | 82S10<br>93415A<br>82S110<br>82LS10<br>82S126                  | HM7640<br>HM7641<br>HM7642<br>HM7643<br>HM7644       | 82S140<br>82S141<br>82S136<br>82S137<br>82S115 **           |

|                                                                     |                                                            | 93419<br>93421<br>93421A<br>93425                      | 82S09<br>82S16<br>82S116<br>82S11                              | HM7699                                               | 82S115 **<br>Signetics                                      |

|                                                                     |                                                            | 93425A<br>93425A<br>93L425<br>93L425<br>93427<br>93431 | 93425A<br>82S111<br>82LS11<br>82S129<br>82S230                 | 2708<br>3101<br>3101A<br>3106/3106A<br>3107/3107A    | 82S2708<br>82S25<br>3101A<br>82S16<br>82S17                 |

|                                                                     |                                                            | 93436<br>93438<br>93441<br>93442<br>93446              | 82S130<br>82S140<br>82S231<br>82S241<br>82S131                 | 3301A<br>3302<br>3304<br>3322<br>3601                | 82S226<br>82S230<br>82S215 **<br>82S231<br>82S231<br>82S126 |

|                                                                     |                                                            | 93448<br>93452<br>93453<br>93454<br>93457<br>93464     | 82S141<br>82S136<br>82S137<br>82S280<br>82S226<br>82S281       | 3602<br>3604<br>3605<br>3621<br>3622<br>3624         | 82S130<br>82S140<br>82S136<br>82S129<br>82S131<br>82S141    |

|                                                                     |                                                            | 93467                                                  | 82S229                                                         | 3625                                                 | 82S137                                                      |

\*\* Not pin-for-pin compatible.

| Hold Part - The | C. Lite and an a state of the second | 出现的 经公司 医子宫的 |                       |                           |                |

|-----------------|--------------------------------------|--------------|-----------------------|---------------------------|----------------|

| Intersil        | Signetics                            | MMI          | Signetics             | National<br>Semiconductor | Signetics      |

| 5501            | 82S25                                | 10149        | GXB10149              |                           |                |

| 5503            | 74S301                               | 6200         | 82S226                | 74187                     | 82S226         |

| 55S08(A)        | 82S10                                | 6201         | 82S229                | 8573                      | 82S126         |

| 55S18(A)        | 82S11                                | 6205         | 82S230                | 8574                      | 82S129         |

| 5523A           | 82S16                                | 6206         | 82S231                | 8582                      | 82S17          |

| 5533A           | 82S17                                | 6275         | 82S290                | 8588                      | 82S23          |

| 5600            | 82S23                                | 6276         | 82S291                | 86L99                     | 82S25          |

| 5603            | 825126                               | 6280         | 82S280                |                           |                |

| 5604A           | 82S130                               | 6281         | 82S281                |                           |                |

| 5605            | 82S140                               | 6300-1       | 82S126                | TI                        | Signetics      |

|                 |                                      |              |                       |                           |                |

| 56S06           | 82S136                               | 6301-1       | 82S129                | 2708                      | 82S2708        |

| 5610            | 82S123                               | 6305-1       | 82S130                |                           | 825400         |

| 5623A           | 82S129                               | 6306-1       | 82S131                |                           | 82S401         |

| 5624            | 82S131                               | 6330         | 82523                 | 10142                     | GXB10142       |

| 5625            | 82S141                               | 6331         | 82S123                | 10144                     | GXB10144/10410 |

| 56S26           | 82S137                               | 6335         | 82S114 **             | 10147                     | GXB10405       |

|                 |                                      | 6340         | 82S140                | 74187                     | 82S226         |

|                 |                                      | 6341         | 82S141                | 74S188                    | 82S23          |

|                 |                                      | 6348         | 82S146                | 74S189                    | 74S189         |

| Motorola        | Signetics                            | 6349         | 82S147                |                           |                |

| 10100           | 01/01/02                             | 6352         | 82S136                | 74S89                     | 74S89          |

| 10139           | GXB10139                             | 6353         | 82S137                | 74S200                    | 74S200         |

| 10140           | GXB10140                             | 6380         | 82S180                | 74S201                    | 74S201         |

| 10142           | GXB10142                             | 6381         | 82S181                | 74S209                    | 82S11/93425A   |

| 10144           | GXB10144/10410                       | 6385         | 82S2708               | 74S270                    | 82S230         |

| 10145           | GXB10145                             |              |                       | 74S287                    | 82S129         |

| 10146/10415     | GXB10415                             | 6530         | 82S17                 | 74S288                    | 82S123         |

| 10147           | GXB10405                             | 6531         | 82S16<br>82S09        | 74S289                    | 3101A          |

| 10148           | GXB10148                             | 6555         |                       | 74S301                    | 74S301         |

| 10149           | GXB10149                             | 6560         | 82S25/3101A<br>74S189 | 74S309                    | 82S10/93415A   |

| 4004A           | 828226                               | 6561         |                       | 74\$370                   | 82S231         |

| 4064            | 82S25                                | 82S100       | 82S100                | 74S387                    | 82S126         |

| 4256            | 82516                                | 82S101       | 82S101                | 74\$472                   | 82S146         |

| 5005            | 82\$126                              |              |                       | 74\$473                   | 82S147         |

| 68708           | 8252708                              |              |                       |                           |                |

\*\* Not pin-for-pin compatible.

cross reference

MOS

| AMD        | Signetics | Fairchild   | Signetics | Intel  | Signetics |

|------------|-----------|-------------|-----------|--------|-----------|

|            |           |             |           |        |           |

| 2102       | 2102      | 2102        | 2102      | 2101   | 2101      |

|            | 21F02     |             | 21F02     |        | 2102      |

|            | 21L02     |             | 21L02     |        | 21F02     |

| 9216       | 2617      | 3343        | 2521      | 2102A  | 21L02     |

| AM1402APC  | 2502      | 3344        | 2522      |        | 2102A     |

| AM1403A    | 2503      | 3347        | 2532      | 2102AL | 2102AL    |

| AM1404A    | 2504      | 3349        | 2518      | 2107B  | 2680      |

| AM1507     | 2517      | 3533        | 2533      | 2111   | 2111      |

| AM1507T    | 2506      | F4720       | HEF4720B  | 2112   | 2112      |

| AM2505K    | 2505      |             |           | 2114   | 2614      |

| AM2806HC   | 2512      |             |           | 2115   | 2115      |

| AM2807PC   | 2524      | General     |           | 2116A  | 2690      |

| AM2808PC   | 2525      | Instruments | Signetics | 2125   | 2125      |

| AM2809     | 2521      | 0500        | 0500      | 2308   | 2607      |

| AM2833PC   | 2533      | 2509        | 2509      | 2316E  | 2616      |

| AM9060     | 2680      | 2510        | 2510      | 2704   | 2704      |

| P1101      | 2501      | 2511        | 2511      | 2704   | 2607      |

| FIIUI      | 2501      | 2513        | 2513      | 2700   | 2708      |

|            |           | 2516        | 2516      | C1402A | 2502      |

| Electronic |           | 2530        | 2530      | C14UZA | 2502      |

| Arrays     | Signetics | 2533        | 2533      | C1403A | 2503      |

| Arrays     | Signetics | 2580        | 2580      | M1404A | 2504      |

| 4600       | 2600      |             |           | M1405A | 2505      |

| 4900       | 2600      |             |           | P1101  | 2501      |

| Intersil | Signetics | Motorola           | Signetics    | Synertex               | Signetics    |

|----------|-----------|--------------------|--------------|------------------------|--------------|

| IM7501   | 2501      | 6570               | 2609         | 2316B                  | 2616         |

| IM7552   | 2102      | 6830               | 2608         | 4600                   | 2600         |

|          | 21F02     |                    |              |                        |              |

|          | 21L02     |                    |              |                        |              |

| IM7712C  | 2512      | National           |              | Texas                  |              |

| IM7722C  | 2525      | Semiconductor      | Signetics    | Instruments            | Signetics    |

| IM7780C  | 2532      | MM1101<br>MM1402A  | 2501<br>2502 | TMS3112NC<br>TMS3120NC | 2518<br>2532 |

| Mostek   | Signetics | MM1403A<br>MM1404A | 2503<br>2504 | TMS3128NC<br>TMS3129NC | 2521<br>2522 |

| 29000    | 2600      | MM1506H            | 2506         | TMS3133NC              | 2533         |

| MK1007P  | 2532      | MM1507H            | 2517         | TMS4035                | 2102         |

| MK4007   | 2501      | MM2102             | 2102         |                        | 21F02        |

|          | 25L01     |                    | 21F02        |                        | 21L02        |

| MK4027   | 2627      |                    | 21L02        | TMS4030                | 2680         |

| MK4096   | 2660      | MM2521             | 2521         | TMS4060                | 2680         |

| MK4102   | 2102      | MM2522             | 2522         |                        |              |

| 102      | 21F02     | MM5058             | 2533         |                        |              |

|          | 21L02     | MM5280             | 2680         |                        |              |

| MK4116   | 2690      |                    |              |                        |              |

## technical data

#### Bipolar

#### Output structure: OC open collector TS three-state

|         | capacity | type      | output<br>structure | no. of<br>pins | tAA<br>max | input<br>current | supply<br>voltage | max<br>supply<br>current | package |

|---------|----------|-----------|---------------------|----------------|------------|------------------|-------------------|--------------------------|---------|

|         |          |           |                     |                | ns         | μΑ               | V                 | mA                       |         |

| TTL-RAM | 16 x 4   | N3101A *  | OC                  | 16             | 35         | 100              | 5                 | 105                      | N, F    |

|         | 16 x 4   | N74S89    | OC                  | 16             | 50         | 100              | 5                 | 105                      | N, F    |

|         | 16 x 4   | N74S189   | TS                  | 16             | 35         | 250              | 5                 | 110                      | N, F    |

|         | 16 x 4   | N82S25    | oc                  | 16             | 50         | 100              | 5                 | 105                      | N, F    |

|         | 256 x 1  | N74S200   | TS                  | 16             | 50         | 100              | 5                 | 130                      | N, F    |

|         | 256 x 1  | N74S201   | TS                  | 16             | 50         | 100              | 5                 | 130                      | N, F    |

|         | 256 x 1  | N74S301   | OC                  | 16             | 50         | 100              | 5                 | 130                      | N, F    |

|         | 256 x 1  | N82S16    | TS                  | 16             | 50         | 100              | 5                 | 115                      | N, F    |

|         | 256 x 1  | N82S17    | OC                  | 16             | 50         | 100              | 5                 | 115                      | N, F    |

|         | 256 x 1  | N82S116   | TS                  | 16             | 40         | 100              | 5                 | 115                      | N, F    |

|         | 256 x 1  | N82S117   | OC                  | 16             | 40         | 100              | 5                 | 115                      | N, F    |

|         | 64 x 9   | N82S09    | OC                  | 28             | 45         | 100              | 5                 | 190                      | N, I    |

|         | 1024 x 1 | N82S10    | OC                  | 16             | 45         | 100              | 5                 | 170                      | N, F    |

|         | 1024 x 1 | N82S11    | TS                  | 16             | 45         | 100              | 5                 | 170                      | N, F    |

|         | 1024 x 1 | N82S110   | OC                  | 16             | 35         | 100              | 5                 | 170                      | N, F    |

|         | 1024 × 1 | N82S111   | TS                  | 16             | 35         | 100              | 5                 | 170                      | N, F    |

|         | 1024 × 1 | N93415A   | OC                  | 16             | 45         | 1.00             | 5                 | 170                      | N, F    |

|         | 1024 × 1 | N93425A   | TS                  | 16             | 45         | 100              | 5                 | 170                      | N, F    |

|         | 1024 x 1 | N82LS10 * | OC                  | 16             | 60         | 100              | 5                 | 60                       | N, F    |

|         | 1024 x 1 | N82LS11 * | TS                  | 16             | 60         | 100              | 5                 | 60                       | N, F    |

|         | 256 x 8  | N82S208   | TS                  | 22             | 60         | 100              | 5                 | 185                      | N, F    |

|         | 256 x 9  | N82S210   | TS                  | 24             | 60         | 100              | 5                 | 185                      | N, F    |

|         | 4096 x 1 | N82S400 * | OC                  | 18             | 70         | 150              | 5                 | 155                      | 1       |

|         | 4096 x 1 | N82S401 * | TS                  | 18             | 70         | 150              | 5                 | 155                      | 1       |

\* In development.

Military versions of industrial ICs with prefix N have S as a prefix. **Example:** industrial version N82S25, military version S82S25. The specifications shown below apply to industrial versions. There is generally some derating in specification for military versions due to the extended temperature range.

Temperature ranges

C 0 to 75 °C M -55 to +125 °C

| chip<br>enable<br>lines | temp.<br>range | pin compatible types<br>= fully compatible | second sourced by                                     | pin diagram<br>on page |

|-------------------------|----------------|--------------------------------------------|-------------------------------------------------------|------------------------|

| 1                       | M,C            | 82S25, 74S89                               | AMD, Intel, MMI, TI                                   | 26                     |

| 1                       | M, C           | N3101A, 82S25                              | TI                                                    | 26                     |

| 1                       | M, C           | -                                          | MML, TI                                               | 26                     |

| 1                       | M, C           | N3101A, 74S89                              | AMD, Fch, Harris, Intel, Intersil, MMI, Mot, National | 26                     |

| 3                       | M,C            | 82S16, 82S116, 74S201 ▲                    | ТІ                                                    | 24                     |

| 3                       | M,C            | 82S16, 82S116, 74S200 A                    | TI                                                    | 24                     |

| 3                       | M, C           | 82S17, 82S117                              | Fch, Intersil, TI                                     | 24                     |

| 3                       | M, C           | 82S116, 74S200, 74S201                     | AMD, Fch, Intel, Intersil, MMI, Mot                   | 24                     |

| 3                       | M,C            | 82S117, 82S301                             | AMD, Fch, Intel, Intersil, MMI                        | 24                     |

| 3                       | С              | 82S16, 74S200, 74S201                      | Fch                                                   | 24                     |

| 3                       | С              | 82S17, 74S301                              | Fch                                                   | 24                     |

| 1                       | M, C           | -                                          | Fch, MMI                                              | 27                     |

| 1                       | M, C           | 82S110, 93415A 🔺, 82LS10                   | AMD, Fch, Intersil, TI                                | 25                     |

| 1                       | M,C            | 82S111,93425A,82LS11                       | AMD, Fch, Intersil, TI                                | 25                     |

| 1                       | С              | 82S10, 93415A, 82LS10                      | Fch                                                   | 25                     |

| 1                       | С              | 82S11, 93425A, 82LS11                      | Fch                                                   | 25                     |

| 1                       | С              | 82S10 A, 82S110, 82LS10                    | AMD, Fch, TI                                          | 25                     |

| 1                       | С              | 82S11 A, 82S111, 82LS11                    | AMD, Fch, TI                                          | 25                     |

| 1                       | С              | 82S10, 93415A, 82S110                      | Fch                                                   | 25                     |

| 1                       | С              | 82S11, 93425A, 82S111                      | Fch                                                   | 25                     |

| 1                       | С              | _                                          |                                                       | 27                     |

| 1                       | С              | -                                          | -                                                     | 27                     |

| 1                       | С              | -                                          | ТІ                                                    | 25                     |

| 1                       | С              | _                                          | TI                                                    | 25                     |

#### technical data

#### Bipolar

Output structure: OC open collector

TS three-state

|          | capacity | type      | output<br>structure | no. of<br>pins | tAA<br>max | input<br>current | supply<br>voltage | max<br>supply | package |

|----------|----------|-----------|---------------------|----------------|------------|------------------|-------------------|---------------|---------|

|          |          |           |                     |                |            |                  | 14                | current       |         |

|          |          |           |                     |                | ns         | μA               | V                 | mA            |         |

| TTL-PROM | 32 x 8   | N82S23    | OC                  | 16             | 50         | 100              | 5                 | 77            | N, F    |

|          | 32 × 8   | N82S123   | TS                  | 16             | 50         | 100              | 5                 | 77            | N, F    |

|          | 256 × 4  | N82S27    | OC                  | 16             | 40         | 1600             | 5                 | 140           | F       |

|          | 256 x 4  | N82S126   | OC                  | 16             | 50         | 100              | 5                 | 120           | N, F    |

|          | 256 x 4  | N82S129   | TS                  | 16             | 50         | 100              | 5                 | 120           | N, F    |

|          | 256 x 8  | N82S114   | TS                  | 24             | 60         | 100              | 5                 | 180           | N, F    |

|          | 512 x 4  | N82S130   | OC                  | 16             | 50         | 100              | 5                 | 140           | N, F    |

|          | 512 x 4  | N82S131   | TS                  | 16             | 50         | 100              | 5                 | 140           | N, F    |

|          | 512 x 8  | N82S115   | TS                  | 24             | 60         | 100              | 5                 | 180           | N, F    |

|          | 512 x 8  | N82S140   | OC                  | 24             | 60         | 100              | 5                 | 175           | N, F    |

|          | 512 x 8  | N82S141   | TS                  | 24             | 60         | 100              | 5                 | 175           | N, F    |

|          | 512 x 8  | N82S146 * | OC                  | 20             | 45         | -                | 5                 | -             | N       |

|          | 512 x 8  | N82S147 * | TS                  | 20             | 45         | -                | 5                 | _             | N       |

|          | 1024 × 4 | N82S136   | OC                  | 18             | 60         | 100              | 5                 | 140           | F       |

|          | 1024 x 4 | N82S137   | TS                  | 18             | 60         | 100              | 5                 | 140           | F       |

|          | 1024 x 8 | N82S180   | OC                  | 24             | 70         | 100              | 5                 | 150           | F       |

|          | 1024 x 8 | N82S181   | TS                  | 24             | 70         | 100              | 5                 | 150           | F       |

|          | 1024 x 8 | N82S2708  | TS                  | 24             | 70         | 100              | 5                 | 150           | F       |

|          | 2048 x 4 | N82S184   | OC                  | 18             | 100        | 100              | 5                 | 120           | 1       |

|          | 2048 × 4 | N82S185   | TS                  | 18             | 100        | 100              | 5                 | 120           | 1       |

|          | 2048 x 8 | N82S190   | OC                  | 24             | 80         | 100              | 5                 | 175           | N, F    |

|          | 2048 x 8 | N82S191   | TS                  | 24             | 80         | 100              | 5                 | 175           | N, F    |

\* In development.

Military versions of industrial ICs with prefix N have S as a prefix. Example: industrial version N82S25, military version S82S25. The specifications shown below apply to industrial versions. There is generally some derating in specification for military versions due to the extended temperature range.

Temperature ranges

C 0 to 75 °C M -55 to +125 °C

-55 to +125 C

| chip<br>enable<br>lines | temp.<br>range | pin compatible types<br>▲ = fully compatible |                                                          | pin diagram<br>on page |

|-------------------------|----------------|----------------------------------------------|----------------------------------------------------------|------------------------|

| 1                       | M,C            | -                                            | AMD, Harris, Intersil, MMI, National, TI                 | 21                     |

| 1                       | M,C            | -                                            | AMD, Harris, Intersil, MMI, TI                           | 21                     |

| 2                       | С              | 82S126, 82S226                               | -                                                        | 19                     |

| 2                       | M,C            | 82S226 A, 82S27                              | AMD, Fch, Harris, Intel, Intersil, MMI, Mot, National, T | 1 19                   |

| 2                       | M,C            | 82S229 <b>▲</b>                              | AMD, Fch, Harris, Intel, Intersil, MMI, National, TI     | 19                     |

| 2                       | M,C            | 82S214 ▲                                     | MMI **                                                   | 21                     |

| 1                       | M, C           | 82S230 A                                     | Fch, Harris, Intel, Intersil, MMI                        | 19                     |

| 1                       | M, C           | 82S231 🔺                                     | Fch, Harris, Intel, Intersil, MMI                        | 19                     |

| 2                       | M, C           | 82S215 ▲                                     | Harris **                                                | 22                     |

| 4                       | M, C           | 82S240 A                                     | Fch, Harris, Intel, Intersil, MMI                        | 22                     |

| 4                       | M, C           | 82S241 ▲                                     | Fch, Harris, Intel, Intersil, MMI                        | 22                     |

| 1                       | С              | -                                            | MMI, TI **                                               | 22                     |

| 1                       | С              | -                                            | MMI, TI **                                               | 22                     |

| 2                       | M, C           |                                              | Fch, Harris, Intel, Intersil, MMI                        | 20                     |

| 2                       | M, C           | _                                            | Fch, Harris, Intel, Intersil, MMI                        | 20                     |

| 4                       | M, C           | 82S280 A                                     | MMI                                                      | 23                     |

| 4                       | M, C           | 82S281 ▲                                     | MMI                                                      | 23                     |

| 1                       | M, C           | -                                            | MMI, (EPROM – Intel, Mot, TI)                            | 23                     |

| 1                       | M, C           | -                                            | -                                                        | 20                     |

| 1                       | M, C           | -                                            | -                                                        | 20                     |

| 3                       | С              | 82S290 <b>▲</b>                              | -                                                        | 23                     |

| 3                       | С              | 82S291 <b>▲</b>                              | _                                                        | 23                     |

### technical data

#### Bipolar

| Output struct |             | en collector<br>em pole | OE open en<br>TS three-sta |                |              |                  |                   |                          |         |

|---------------|-------------|-------------------------|----------------------------|----------------|--------------|------------------|-------------------|--------------------------|---------|

|               | capacity    | type                    | output<br>structure        | no. of<br>pins | tAA<br>max   | input<br>current | supply<br>voltage | max<br>supply<br>current | package |

|               |             |                         |                            |                | ns           | μA               | V                 | mA                       |         |

| TTL-ROM       | 256 x 4     | N82S226                 | OC                         | 16             | 50           | 100              | 5                 | 120                      | N, F    |

|               | 256 x 4     | N82S229                 | TS                         | 16             | 50           | 100              | 5                 | 120                      | N, F    |

|               | 256 x 8     | N82S214                 | TS                         | 24             | 60           | 100              | 5                 | 175                      | F       |

|               | 512 x 4     | N82S230                 | OC                         | 16             | 50           | 100              | 5                 | 135                      | F       |

|               | 512 x 4     | N82S231                 | TS                         | 16             | 50           | 100              | 5                 | 135                      | F       |

|               | 512 x 8     | N82S215                 | TS                         | 24             | 60           | 100              | 5                 | 175                      | F       |

|               | 512 x 8     | N82S240                 | OC                         | 24             | 60           | 100              | 5                 | 175                      | F       |

|               | 512 x 8     | N82S241                 | TS                         | 24             | 60           | 100              | 5                 | 175                      | F       |

|               | 1024 x 4    | N8228                   | TP                         | 16             | 70           | 400              | 5                 | 170                      | F, I    |

|               | 1024 x 8    | N82S280                 | OC                         | 24             | 70           | 100              | 5                 | 150                      | 1       |

|               | 1024 x 8    | N82S281                 | TS                         | 24             | 70           | 100              | 5                 | 150                      | 1       |

|               | 2048 x 8    | N82S290                 | OC                         | 24             | 70           | 100              | 5                 | 170                      | F       |

|               | 2048 x 8    | N82S291                 | TS                         | 24             | 70           | 100              | 5                 | 170                      | F       |

| TTL-SAM       | 8 x 4       | N82S12                  | OC                         | 24             |              |                  | 5                 |                          |         |

| TTL-SAM       | 8 x 4       | N82S12                  | TS                         | 24             | 35<br>35     | 250<br>250       | 5                 | 160<br>160               | N, F    |

|               |             |                         |                            |                |              |                  |                   |                          | N, F    |

| TTL-WWRN      |             | N82S21                  | OC                         | 16             | 50           | 1600             | 5                 | 130                      | N, F    |

| TTL-FPLA      |             | N82S100                 | TS                         | 28             | 50           | 100              | 5                 | 170                      | N, ľ    |

|               | 16 x 48 x 8 | N82S101                 | OC                         | 28             | 50           | 100              | 5                 | 170                      | N, I    |

|               | 16 x 48 x 8 | N82S106                 | OC                         | 28             | 50           | 100              | 5                 | 170                      | N, I    |

|               | 16 x 48 x 8 | N82S107                 | TS                         | 28             | 50           | 100              | 5                 | 170                      | N, I    |

| TTL-FPGA      | 16 x 9      | N82S102                 | OC                         | 28             | 30           | 100              | 5                 | 170                      | N, I    |

|               | 16 x 9      | N82S103                 | TS                         | 28             | 30           | 100              | 5                 | 170                      | N, I    |

| TTL-PLA       | 16 x 48 x 8 | N82S200                 | TS                         | 28             | 50           | 100              | 5                 | 170                      | N, I    |

|               | 16 x 48 x 8 | N82S201                 | OC                         | 28             | 50           | 100              | 5                 | 170                      | N, I    |

| ECL-RAM       | 64 x 1      | GXB10140                | OE                         | 1-00           | CHOICE STORE |                  |                   |                          |         |

| LOL-NAM       | 64 x 1      | GXB10140<br>GXB10142    | OE                         | 16<br>16       | 15           | 265              | 5,2               | 80 (typ)                 | D, P    |

|               | 64 x 1      | GXB10142<br>GXB10148    | OE                         | 16             | 10<br>15     | 265<br>265       | 5,2<br>5,2        | 100                      | D, P    |

|               | 16 x 4      | GXB10145                | OE                         | 16             | 15           | 200              | 5,2               | 80 (typ)<br>145          | D, P    |

|               |             |                         |                            |                |              |                  |                   |                          | D, P    |

|               | 128 x 1     | GXB10405                | OE                         | 16             | 15           | 200              | 5,2               | 110                      | E       |

|               | 256 x 1     | GXB10144                | OE                         | 16             | 30           | 200              | 5,2               | 112                      | D, E    |

|               | 256 x 1     | GXB10410                | OE                         | 16             | 35           | 220              | 5,2               | 125                      | E       |

|               | 1024 x 1    | GXB10415 *              | OE                         | 16             | 25           | -                | 5,2               | -                        | E       |

| ECL-PROM      | 32 x 8      | GXB10139                | OE                         | 16             | 20           | 265              | 5,2               | 145                      | D       |

|               | 256 x 4     | GXB10149                | OE                         | 16             | 20           | 265              | 5,2               | 150                      | D, E    |

| ECL-CAM       | 8 x 2       | GXB10155                | OE                         | 18             | 13           | 220              | 5,2               | 140                      | E       |

\* In development.

Military versions of industrial ICs with prefix N have S as a prefix, **Example:** industrial version N82S25, military version S82S25. The specifications shown below apply to industrial versions. There is generally some derating in specification for military versions due to the extended temperature range.

Temperature ranges

$\begin{array}{rrrr} TTL - C - & 0 \ to \ 75 \ ^{\circ}C \\ TTL - M - & -55 \ to \ +125 \ ^{\circ}C \\ ECL - C - & -30 \ to \ + \ 85 \ ^{\circ}C \end{array}$

| chip<br>enable<br>lines | temp.<br>range | pin compatible types<br>▲ = fully compatible | second sourced by                  | pin diagram<br>on page |

|-------------------------|----------------|----------------------------------------------|------------------------------------|------------------------|

| 2                       | M, C           | N82S126 A, N82S27                            | Fch, Intel, MMI, Mot, National, TI | 19                     |

| 2                       | M, C           | N82S129 ▲                                    | Fch, MMI                           | 19                     |

| 2                       | M,C            | N82S114                                      | -                                  | 21                     |

| 1                       | M, C           | N82S130 ▲                                    | Fch, Intel, MMI, TI                | 19                     |

| 1                       | M,C            | N82S131 ▲                                    | Fch, Intel, MMI, TI                | 19                     |

| 2                       | M,C            | N82S115 ▲                                    | -                                  | 22                     |

| 4                       | С              | N82S140 A                                    | -                                  | 22                     |

| 4                       | C              | N82S141 ▲                                    | Fch                                | 22                     |

|                         | С              | -                                            | -                                  | 20                     |

| 4                       | M,C            | N82S180 ▲                                    | Fch, MMI                           | 23                     |

| 4                       | M,C            | N82S181 ▲                                    | Fch, MMI                           | 23                     |

| 3                       | С              | N82S190 A                                    | MMI                                | 23                     |

| 3                       | С              | N82S191 ▲                                    | MMI                                | 23                     |

| 2 wr. en.               | С              | _                                            | -                                  | 28                     |

| 2 wr. en.               | С              | -                                            | -                                  | 28                     |

| -                       | С              | -                                            | -                                  | 28                     |

| 1                       | M,C            | N82S200 A                                    | AMD, MMI                           | 29                     |

| 1                       | M, C           | N82S201 ▲                                    | AMD, MMI                           | 29                     |

| _                       | С              | -                                            | -                                  | 29                     |

| -                       | С              | -                                            | -                                  | 29                     |

| 1                       | M,C            | -                                            | -                                  | 29                     |

| 1                       | M,C            | -                                            | -                                  | 29                     |

| 1                       | M,C            | N82S100                                      | -                                  | 29                     |

| 1                       | M,C            | N82S101                                      | -                                  | 29                     |

| 2                       | С              | GXB10142, GXB10148                           | Mot                                | 24                     |

| 2                       | С              | GXB10140, GXB10148                           | Mot, TI                            | 24                     |

| 2                       | С              | GXB10140, GXB10142                           | Mot                                | 24                     |

| 1                       | С              | _                                            | Fch, Mot                           | 26                     |

| _                       | С              | -                                            | Mot, TI                            | 24                     |

| 3                       | C              | GXB10410                                     | Fch, Mot, TI                       | 24                     |

| 3                       | C              | GXB10144                                     | Fch, Mot, TI                       | 24                     |

| -                       | С              | -                                            | Fch, Mot                           | 25                     |

| 1                       | С              | _                                            | Mot                                | 21                     |

| 1                       | C              | _                                            | Fch, Harris, MMI, Mot              | 19                     |

|                         | С              |                                              |                                    | 28                     |

technical data

MOS

|                    | capacity    | type        | no. of | taa                      | supply             |

|--------------------|-------------|-------------|--------|--------------------------|--------------------|

|                    |             |             | pins   | typ                      | voltage            |

|                    |             |             |        | ns                       | V                  |

| Static RAM         | 256 x 1     | 2501        | 16     | 1000                     | +5, -9             |

|                    | 256 x 1     | 25L01       | 16     | 1000                     | +5, -12            |

|                    | 256 x 4     | 2101        | 22     | 450 - 1000               | +5                 |

|                    | 256 × 4     | 2111        | 18     | 450 - 1000               | +5                 |

|                    | 256 x 4     | 2112        | 16     | 450 - 1000               | +5                 |

|                    | 256 × 4     | 2606        | 16     | 750                      | +5                 |

|                    | 256 x 4     | 2606-1      | 16     | 500                      | +5                 |

|                    | 1024 × 1    | 2102        | 16     | 500 - 1000               | +5                 |

|                    | 1024 × 1    | 21F02       | 16     | 250 - 450                | +5                 |

|                    | 1024 x 1    | 21L02       | 16     | 400 - 1000               | +5                 |

|                    | 1024 × 1    | 2102A/AL    | 16     | 150 - 650                | +5                 |

|                    | 1024 × 1    | 2115        | 16     | 35 - 75                  | +5                 |

|                    | 1024 x 1    | 2125        | 16     | 35 - 75                  | +5                 |

|                    | 1024 x 4    | 2614 *      | 18     |                          | +5                 |

|                    | 1024 x 4    | 2624 *      | 18     |                          | +5                 |

|                    | 4096 × 1    | 2613 *      | 18     |                          | +5                 |

|                    | 4096 x 1    | 2623 *      | 18     |                          | +5                 |

| LOCMOS static RAM  | 256 × 1     | HEF4720B(V) | 16     | <b>150</b> – 450         | +3 to +15          |

| Dynamic RAM        | 4096 × 1    | 2660        | 16     | 200 - 350                | +12, +5, -         |

|                    | 096 × 1     | 2680        | 22     | <b>200</b> - <b>3</b> 50 | -12,+ <b>5</b> ,-) |

|                    | - 196 × 1   | 2627        | 16     | 150 - 250                | +12, +5,           |

|                    |             | 2390 *      |        | 150 - 250                | 12, +5,            |

| ROMs and character | 512 × 8     | 2530        | 24     | 700                      | +5, -12            |

| generators         | 2048 × 4    | 2580        | 24     | 950                      | +5, -12            |

| o-channel          | 64 x 8 x 5  | 2513        | 24     | 600                      | +5, -12            |

|                    | 64 x 6 x 8  | 2516        | 24     | 600                      | +5, -12            |

|                    | 64 x 9 x 9  | 2526        | 24     | 700                      | +5, -12            |

| n-channel          | 1024 × 8    | 2607        | 24     | 450                      | +5                 |

|                    | 1024 x 8    | 2608        | 24     | 550                      | +5                 |

|                    | 2048 x 8    | 2600        | 24     | 300                      | +5                 |

|                    | 2048 x 8    | 2616        | 24     | 300                      | +5                 |

|                    | 2048 × 8    | 2617        | 24     | 450                      | +5                 |

|                    | 4096 × 8    | 2632 *      | 24     |                          | +5                 |

|                    | 4096 × 8    | 2633 *      | 24     |                          | +5                 |

|                    | 128 x 7 x 9 | 2609        | 24     | 500                      | +5                 |

| EPROM              | 4096        | 2704        | 24     | 450                      | +12, +5, -         |

|                    | 8192        | 2708        | 24     | 450                      | +12, +5, -5        |

\* In development.

| Temperature range                    |

|--------------------------------------|

| C = 0 to +70 °C                      |

| $XC = -40 \text{ to } +85 \degree C$ |

| chip   | temp. | pin                    | second sourced by                               | pin diagram |

|--------|-------|------------------------|-------------------------------------------------|-------------|

| enable | range | compatible             |                                                 | on page     |

| ines   |       | types                  |                                                 |             |

| -      | С     | 25L01                  | AMD, Intel, Intersil, Mostek, National          | 30          |

| 1      | С     | 2501                   | Mostek                                          | 30          |

| 2      | С     | -                      | Intel                                           | 3:          |

| 2      | С     | _                      | Intel                                           | 3:          |

| 1      | С     | -                      | Intel                                           | 33          |

| 1      | С     | 2606-1                 | -                                               | 3           |

| 1      | С     | 2606                   |                                                 | 3.          |

| 1      | С     | 21F02, 21L02, 2102A/AL | -                                               | 3           |

| 1      | C     | 2102, 21L02, 2102A/AL  | AMD, Fch, Intel, Intersil, Mostek, National, TI | 3           |

| 1      | С     | 2102, 21F02, 2102A/AL  |                                                 | 3           |

| 1      | С     | 2102, 21F02, 21L02     | Intel                                           | 3           |

| 1      | С     | 2125                   | Intel                                           | 3           |

| 1      | С     | 2115                   | Intel                                           | 3           |

| _      | С     | 2624                   | Intel                                           | 3           |

|        | С     | 2614                   | Intel                                           | 3           |

| -      | С     | 2623                   | Intel                                           | 3           |

| -      | С     | 2613                   | Intel                                           | 3           |

| 1      | XC    | -                      | Fch                                             | 3           |

| 1      | С     | -                      | Mostek                                          | 3           |

| 1      | С     | -                      | AMD, Intel, National, TI                        | 3           |

| 1      | С     | -                      | Mostek                                          | 3           |

| 1      | С     | -                      | Intel, Mostek                                   | 3           |

| 1      | С     | -                      | GI                                              | 3           |

| 4      | С     | -                      | GI                                              | 3           |

| 1      | С     |                        | GI                                              | 3           |

| 1      | C     | -                      | GI                                              | 3           |

| 1      | С     | -                      | -                                               | 3           |

| 2      | С     | _                      | Intel                                           | 3           |

| 4      | С     | -                      | Motorola                                        | 3           |

| 2      | С     | -                      | Electronic Arrays, Mostek, Synertex             | 3           |

| 3      | С     | -                      | Intel, Synertex                                 | 3           |

| 3      | С     | -                      | AMD                                             | 3           |

| _      | С     | -                      | -                                               | 3           |

| -      | С     | _                      | will be industry standard                       | -           |

| 4      | С     | -                      | Motorola                                        | 3           |

| 1      | С     | -                      | Intel                                           | 3           |

| 1      | C     |                        | Intel                                           | 3           |

#### technical data

#### MOS

Several types can be made available in Cerdip (F package) and metal ceramic (I package).

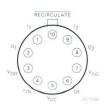

#### Static shift registers — one clock (TTL compatible) — power supplies +5 and -12 V; 2509/10/11 also -5 V

| capacity      | type | output      | on-chip     | package | typ          | second sourced by         | pin diagram |

|---------------|------|-------------|-------------|---------|--------------|---------------------------|-------------|

|               |      | structure   | recirculate | leads   | speed<br>MHz |                           | on page     |

| hex 32 bits   | 2518 | bare drain  | yes         | N-16    | 3,0          | Fch, Tl                   | 40          |

| hex 40 bits   | 2519 | bare drain  | yes         | N-16    | 3,0          | -                         | 40          |

| dual 50 bits  | 2509 | three-state | yes         | N-14, K | 3,0          | GI                        | 40          |

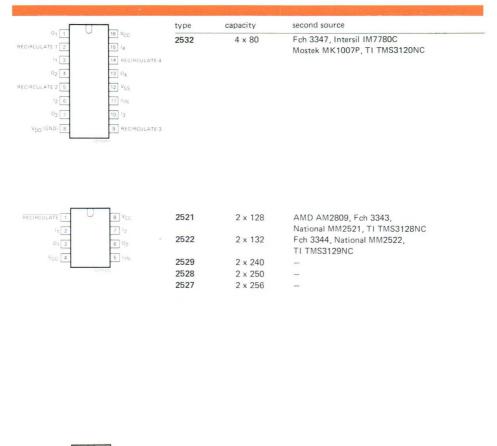

| quad 80 bits  | 2532 | push-pull   | yes         | N-16    | 3,0          | Fch, Intersil, Mostek, TI | 41          |

| dual 100 bits | 2510 | three-state | yes         | N-14, K | 3,0          | GI                        | 40          |

| dual 128 bits | 2521 | push-pull   | yes         | N-8     | 3,0          | AMD, Fch, National, TI    | 41          |

| dual 132 bits | 2522 | push-pull   | yes         | N-8     | 3,0          | Fch, National, TI         | 41          |

| dual 200 bits | 2511 | three-state | yes         | N-14, K | 3,0          | GI                        | 40          |

| dual 240 bits | 2529 | push-pull   | yes         | N-8     | 3,0          |                           | 41          |

| dual 250 bits | 2528 | push-pull   | yes         | N-8     | 3,0          |                           | 41          |

| dual 256 bits | 2527 | push-pull   | yes         | N-8     | 3,0          | —                         | 41          |

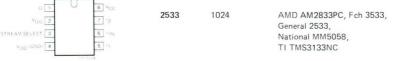

| 1024 bits     | 2533 | push-pull   | jumper      | N-8     | 2,0          | AMD, Fch, GI, National,   | TI 41       |

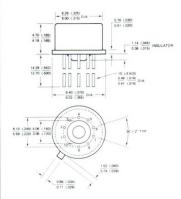

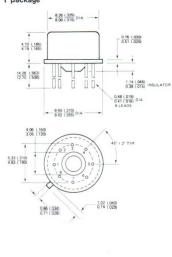

#### Dynamic shift registers – two clocks (not TTL compatible) – power supplies +5 and –5 V

|               | - F  | sower suppries . | J and J V |         |      |                      |    |

|---------------|------|------------------|-----------|---------|------|----------------------|----|

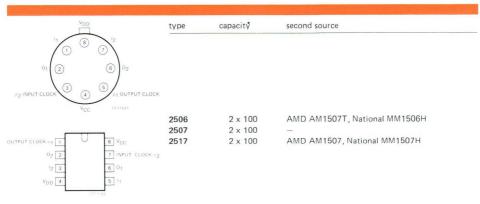

| dual 100 bits | 2517 | 20 kΩ PD         | no        | T, N-8  | 4,0  | AMD, National        | 42 |

| dual 100 bits | 2507 | 7,5 kΩ PD        | no        | T, N-8  | 4,0  |                      | 42 |

| dual 100 bits | 2506 | bare drain       | no        | T, N-8  | 4,0  | AMD, National        | 42 |

| quad 256 bits | 2502 | bare drain       | no        | N-16    | 10,0 | AMD, Intel, National | 42 |

| 512 bits      | 2524 | bare drain       | yes       | N-8     | 5,0  | AMD                  | 42 |

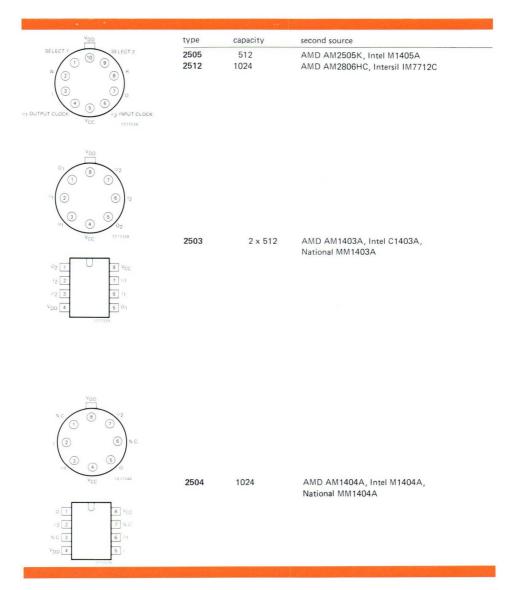

| 512 bits      | 2505 | bare drain       | yes       | К       | 3,0  | AMD, Intel           | 43 |

| dual 512 bits | 2503 | bare drain       | no        | TA, N-8 | 10,0 | AMD, Intel, National | 43 |

| 1024 bits     | 2525 | bare drain       | yes       | N-8     | 5,0  | AMD, Intersil        | 42 |

| 1024 bits     | 2512 | bare drain       | yes       | К       | 3,0  | AMD, Intersil        | 43 |

| 1024 bits     | 2504 | bare drain       | no        | TA, N-8 | 10,0 | AMD, Intel, National | 43 |

|               |      |                  |           |         |      |                      |    |

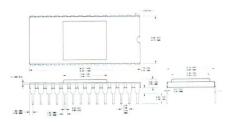

#### pin diagrams — second sources

Bipolar

#### ROMs and PROMs 4 bits wide

|     | -1_                | type    | capacity/output structure | second source                       |

|-----|--------------------|---------|---------------------------|-------------------------------------|

| 6 1 | 16 V <sub>CC</sub> | 82827   | 256 x 4 PROM/OC           | -                                   |

| 5 2 | 15 A 7             | 82\$126 | 256 x 4 PROM/OC           | AMD 27S10, Fch 93417,               |

| 1 3 | 14 CE2             |         |                           | Harris 1024A/7611, Intel 3601,      |

| 3 4 | 13 CE 1            |         |                           | Intersil 5603, MMI 6300-1,          |

| 5   | 12 01              |         |                           | Mot 5005, National 8573, TI 74S387  |

| 6   | 11 02              | 82\$129 | 256 x 4 PROM/TS           | AMD 27S11, Fch 93427,               |

|     |                    |         |                           | Harris 1024/HM7610, Intel 3621,     |

| 7   | 10 O3              |         |                           | Intersil 5623A, MMI 6301-1,         |

| 8   | 9 04               |         |                           | National 8574, TI 74S287            |

| -   | 12 ( /268          | 82S226  | 256 x 4 ROM/OC            | Fch 93406, Intel 3301A,             |

|     |                    |         |                           | MMI 6200, Mot 4004A, National 74187 |

|     |                    | 828229  | 256 x 4 ROM/TS            | TI 74187                            |

|     |                    |         |                           | Fch 93467, MMI 6201                 |

| A6 1  | 16 V <sub>CC</sub> | 82\$130 | 512 x 4 PROM/OC | Fch 93436, Harris HM7620,  |

|-------|--------------------|---------|-----------------|----------------------------|

| A 5 2 | 15 A7              |         |                 | Intel 3602,                |

| A4 3  | 14 A8              |         |                 | Intersil 5604A, MMI 6305-1 |

| A3 4  | 13 CE              | 82\$131 | 512 x 4 PROM/TS | Fch 93446, Harris HM7621,  |

|       |                    |         |                 | Intel 3622,                |

| A0 5  | 12 01              |         |                 | Intersil 5624, MMI 6306-1  |

| A1 6  | 11 O2              | 82\$230 | 512 x 4 ROM/OC  | Fch 93431, Intel 3302,     |

| A2 7  | 10 03              |         |                 | MMI 6205, TI 74S270        |

|       |                    | 82\$231 | 512 x 4 ROM/TS  | Fch 93441, Intel 3322,     |

| GND 8 | 9 04               | 020201  | OTE X THOM, TO  | MMI 6206, TI 74S370        |

|       | 1277270            |         |                 | 10101 0200, 11 740070      |

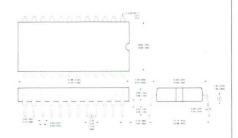

### pin diagrams - second sources

Bipolar

#### ROMs and PROMs 4 bits wide

|                      | type | capacity/output structure | second source |

|----------------------|------|---------------------------|---------------|

| 1 16 V <sub>CC</sub> | 8228 | 1024 x 4 ROM/TP           | -             |

| 3 14 A8              |      |                           |               |

| 4 13 A <sub>9</sub>  |      |                           |               |

| 5 12 01              |      |                           |               |

| 6 11 O <sub>2</sub>  |      |                           |               |

| 7 10 03              |      |                           |               |

| 8 9 O <sub>4</sub>   |      |                           |               |

| 82\$136 | 1024 × 4 PROM/OC | Fch   |

|---------|------------------|-------|

|         |                  | Intel |

|         |                  | MMI   |

| 82\$137 | 1024 x 4 PROM/TS | Fch   |

|         |                  | Inte  |

|         |                  |       |

Fch 93452, Harris HM7642, Intel 3605, Intersil 56S06, MMI 6352 Fch 93453, Harris HM7643, Intel 3625, Intersil 56S26, MMI 6353

\_

| A6             | 1 | U | 18 V <sub>CC</sub> |

|----------------|---|---|--------------------|

| Α5             | 2 |   | 17 A7              |

| A4             | 3 |   | 16 <sup>A</sup> 8  |

| A3             | 4 |   | 15 Ag              |

| A <sub>0</sub> | 5 | • | 14 01              |

| A 1            | 6 |   | 13 O <sub>2</sub>  |

| A <sub>2</sub> | 7 |   | 12 03              |

| A10            | 8 |   | 11 04              |

| SND            | 9 |   | 10 CE              |

| 82\$184 | 2048 x 4 PROM/OC |

|---------|------------------|

| 82S185  | 2048 x 4 PROM/TS |

| 80 1 16 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                   | type                           | capacity/output structure                                 | second source                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|